|

|

常见信号质量问题、危害及解决方法 v. ^, t- x0 w/ q5 o9 u

1 y5 _+ }. p/ s4 H) @

; P& K; r2 y2 {* g' X$ ?. K8 u9 _概述:在电路设计中,“信号”始终是工程师无法绕开的一个知识点。不管是在设计之初,还是在测试环节中,信号质量问题都值得关注。' o. @0 z1 C/ |$ f+ Y7 h' A# R

% D7 ]( B w+ _/ a n0 S2 a o; N( R% P本文主要介绍了信号相关的四类问题:信号过冲、毛刺(噪声)、回沟(台阶)、信号边沿缓慢。; w; y" W4 T$ L8 d' k8 E! p1 T

一、信号过冲2 d* R2 u1 t. l, d. [

如下图所示,这是信号过冲的常见波形图:; Z8 C. e! \. @6 m% h

4 R5 P. Y( l7 S A8 A/ |% C* H

, n; i- @' S% W; Y9 j1 u

, n; i- @' S% W; Y9 j1 u

危害:, z9 ?6 [ g2 _( L$ I

1、超过正常供电范围,会产生闩锁效应(现在由于厂家工艺改进, 闩锁问题基本上可以得到规避。但是长时间的信号过冲会使得器件失效率增加);( z4 ?4 N5 m1 d% h& M; v4 Y# W K( q- t$ s

+ D! j O1 m4 d+ f: q/ F6 k$ R

2、形成干扰源, 对其它器件造成串扰;# b& b# B; a- Q+ I+ ]

: F) ~2 v) U8 o3、管脚上的负电压可能使器件PN衬底( 寄生二极管) 前向偏置,流过的大电流过大时,熔断键丝产生开路。7 ^) [* V; h" i0 T8 Q

4 S! o) }: m) E

产生原因:

0 M- z; _$ l- I1、 其它相邻信号串扰

% {' l3 V* Y# d1 o% o

2 \! p* ?5 P* O8 Y2、 器件驱动能力太强- ?6 A6 r Z% A4 W

* M; U4 y: I* o4 F; ]5 P3、 没有匹配或者匹配不当+ N! }5 v/ R$ T' N2 Z& C

9 |* e, u1 W! D, v0 e. ?

解决方法:

" C; U/ r1 w3 Y1、 PCB布线避开干扰源和耦合路径;

0 s. F4 V4 v( [" B' e2 r$ `, o J: J2 h2 ~$ D: l

2、 增加电阻匹配,参考做法是源端串电阻或者末端并电阻,减 少过冲;' G9 l+ ]8 c! N/ V% E

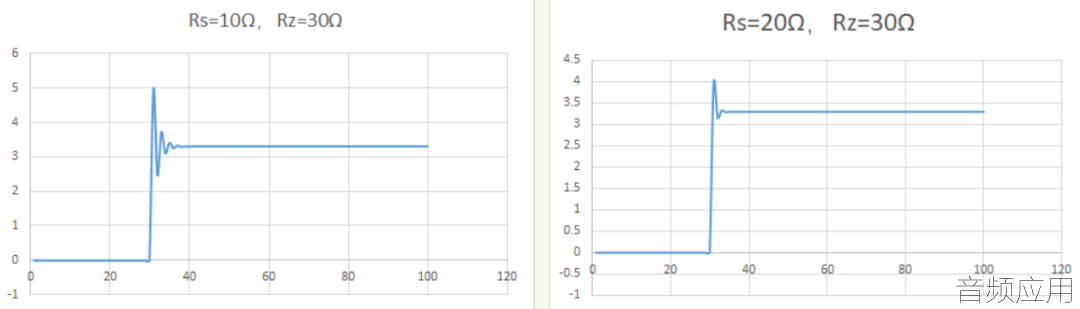

* g/ r, z$ @" t: z; }1 O, m如下图是不同匹配电阻下同一信号的上升沿波形,可以看出,通过调节源端匹配电阻,可以减缓信号上升沿。! J7 u6 \ P1 N+ q" J

! M4 Z# O3 r2 M e

^$ N* [/ ?& c# R* y

0 J R! Q9 N. u+ F, S

, I; D. w+ a7 k. a6 O% d

, I; D. w+ a7 k. a6 O% d

二、毛刺(噪声)

. R( ]- Z3 t$ o$ \, X& t, u如下图所示,这是毛刺的常见波形图:

* M/ I. R6 m- f4 t0 d+ n6 Z4 t2 A

6 e" V5 u' n: h. T% R* V- @$ y

6 e" V5 u' n: h. T% R* V- @$ y

危害:

% K% e5 B; {8 {+ P( P7 E' y容易造成控制信号控制错误或时钟信号相位发生错误:) x2 c8 \- H r8 y

4 T1 P* k" s b* t) u' B& k6 V1、数据线上的毛刺如果被采样到,可能造成判断结果错误;$ A# K( R% G' I: _

; ]5 S4 r, h3 }% X" v! Z# U8 f! p2、边沿触发的器件中,时钟线上的毛刺可能会使得采样到多余的数据 (相当于多了一拍时钟)。

6 L) R5 D- g0 o! k

3 v/ K8 H: w6 K, w* I* `产生原因:

" b4 q. I& B: c/ U/ C" J, l2 p1、PCB走线串扰(例如数据线和时钟线并行走线较长,信号线放置在晶振等干扰源附近);; T4 {' {6 N8 s4 x( K

9 t5 }5 B% d! r2 z" r' ^2、外界干扰,如地线噪声等;

+ `& H, e& F* S7 C- z' M1 e* u6 ]% c2 }' K

3、逻辑出现竞争、冒险。- ^& B; I) V' V% ?) x

" b; Q& s$ Z) L. O+ Y) i( n

注:两个输入信号同时向相反方向的逻辑电平跳变的现象(即一个由1---> 0, 另一个从0 ---> 1),称为竞争。因竞争导致在输出端可能产生尖峰脉冲的现象,称为冒险。

( `: Y' o1 _; [% u. `! W, N8 A

7 ^- `' z9 k+ M* k6 R' I+ Y解决方法:# n: w* b7 ~* H* p

1、控制器件布局和PCB走线,信号远离干扰源;; @; a# Y# x. o4 _( U6 a

( ^& t! x# t- x+ O! S2 c2 `2、添加去耦电容或输出滤波等,滤波器件尽量靠近信号管脚;" [' ^( r; e, E% T6 J: S' Y, c

2 z& o! n7 I, t1 @3、逻辑设计中添加冗余项,或者采用同步逻辑设计,避免竞争冒险。

# m+ n! n- W$ m" K% w R, o4 R# q8 b) [! x3 `5 u

三、回勾(台阶)- U+ k- M' |9 A% {% a# @7 `

如下图所示,这是回沟、台阶的常见波形图:+ G; x7 l' U& k6 k

! u" [, k) U9 f1 q2 [

& s5 X; k/ O# F1 l; \& g, h* m/ _危害:: W! G7 H+ }2 A0 m/ J; _

1、主要是时钟类信号上的回勾有危害, 可能会使得采样到多余的数据(相当于多了一拍时钟),影响了时钟信号上升沿和下降沿的单调性;3 k. W$ D O: z& H! u/ e6 a7 s

/ ?& v. \; y. t- S

2、对于电源信号,上电边沿的回勾可能导致系统死机,需要结合复位信号判断是否可以接受;

, |" k% I, ?1 w6 b6 I0 a

7 T( l! n' z- P- T3 T( r" n3 M3、数据信号由于一般是在数据的中间采样,回勾的影响不是很大(除非速率很高,建立保持时间1~2ns,这时需要考虑回勾对数据的影响)。

" b. a# d) q- ^+ X/ i* t3 d2 b% r9 I- [3 Q

产生原因:

~! c$ U' _/ u9 S/ @匹配不当, 信号放射回来形成回勾。

6 @9 C4 w2 t- s/ ~6 o3 v

* q# E* y7 B4 V# H% x解决方法:

! q# s- o; ]4 U0 P- u增加合适的匹配电阻。

$ j8 j' }0 N! \3 K" @" Z9 ~+ m. \

& L f4 o. T9 |. `# w8 V& Y四、信号边沿缓慢# w; s) t5 ]3 B. d) J

由于驱动不足或者负载过大,信号边沿缓慢常常伴随着信号幅度较低现象。; o9 g; j. g$ i, |6 b

# W4 u& ~' d1 d- L1 ~如下图所示,这是振荡的常见波形图:, H# \$ k7 n1 T) Z8 c

; x% [ \" d, m) N+ \( W& N危害:

* ` B* ~" T- i9 u/ {! {* ?上升、下降沿缓慢发生在数据信号线上(串口信号线,HW信号线等)时,会造成数据采样错误。

1 S2 E1 k8 n* e5 h" ~$ u U t+ R0 A: y n$ u. }0 h7 y" N1 B4 e

产生原因:# ~# B' E% h2 ?1 {2 z

驱动能力不够,或者负载过大(例如链路阻抗太大)。

6 \* ^4 E9 B! L! L/ W" C

/ ?& U' \0 a X7 L X0 l+ p解决方法:" V0 Y4 a! c9 J5 R

1、提高驱动能力

" V8 d1 {2 W) q- |' t3 `" ~- b# ~( ~

2、减小负载 |

|