|

|

楼主 |

发表于 2010-5-8 18:40:35

|

显示全部楼层

1.4 A/D采样模块与DSP数据处理模块接口设计8 z+ G7 }. }0 l/ K

4片PCM4204芯片与TMS320C6713的McASP1相连接,其连接示意图如图4所示。# F, r) z5 k# A- G9 w, E* v

t3 @" V) p2 ~. w1 W

' e: [( b3 B4 d* I$ }1 I# ~( l

6 r2 S' `3 z1 }' b, A3 W, J( B: h- Z

) n- W) @# [* c p p/ v( S, j 图4中,PCM4204 A采用主动工作模式,PCM4204B、PCM4204C和PCM4204D采用被动工作模式。系统采用I2S数据格式,PCM4204A的SDOUT1输出的是1和2通道的数据,SDOUT2输出的是3和4通道的数据;PCM4204B的SDOUT1输出的是5和6通道的数据,SDOUT2输出的是7和8通道的数据;PCM4204C的SDOUT1输出的是9和10通道的数据,SDOUT2输出的是11和12通道的数据;PCM4204D的SDOUT1输出的是13和14通道的数据,SDOUT2输出的是15和16通道的数据。

' _; P. V9 z0 |4 s) B! @ 通过配置芯片引脚S/M、FMT2、FMT1、FMT0、FS2、FS1和:FS0对PCM4204进行设置。

$ P1 v& Y3 X' T0 } 1.5 DSP数据处理模块USB接口设计) f1 U% _" q2 P; p

TMS320C6713通过EMIF的CE3存储空间可以外扩USB2.0接口,因此在对外扩USB进行读/写访问前,需要通过EMIF的CE3控制寄存器CE3C-TL来配置CE3空间存储器接口的类型、存储器宽度及读写时序。CY7C68001采用并行异步存储器接口通过可编程逻辑芯片CPLD与TMS320C6713相连,其原理框图如图5所示。: v9 W. d1 Y7 D" s

7 c, Q/ q' X1 x, e# t

5 Y9 m+ @6 T" k7 Z

' v! R( W8 Y6 N4 U* x* \ Z/ n6 M/ Y& U

和4个状态信号 S# L; ] q( [: M9 t1 h: Q( ~7 J

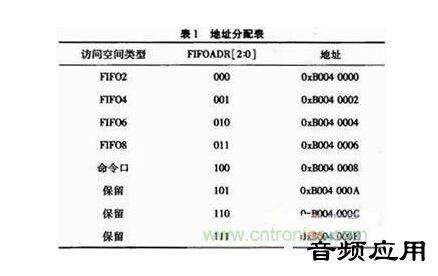

。中断信号 采用TMS320C6713的外部中断EXT_INT6。TMS320C6713使用CY7C68001作为从设备。在这种模式下,DSP可以像读/写普通FIFO一样对CY7C68001内部的FIFO进行读/写。PC主机发出命令的同时也由CY7C68001 的引脚提供中断触发信号给DSP的EXT_INT6。其上升沿被检测到后,DSP就进入相应中断服务程序,开始处理USB的传输。DSP通过EA[4:2]连接FIFOA[2:0]对CY7C68001内部FIFO或命令口进行选择。读/写数据通过ED[15:0]与FIFO[15:0]连接进行。FIFO和命令口的选择和地址分配如表1所示。

* k* c' T" q$ f8 m1 ]9 w( |4 N( x4 g, _& ?, s

4 z% a- ] w$ s3 z/ ^

5 q# y- T' Z; P

, X: B4 f3 t- J; s2 J/ E, x 经实验验证,USB异步传输速率可达3 Mbit?s-1,满足系统需求。# x1 A" K1 w0 _$ ]4 m# I1 `- K

1.6 PC机平台

: P" ?7 d2 m3 X6 U7 p; P7 Z. Z DSP数据处理模块通过USB接口与PC机相连,通过CY7C68001芯片,将前端采集的数据传输到PC机,方便对数据的进一步处理。 |

|